**HDL Coder**™

User's Guide

# MATLAB&SIMULINK®

## **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

HDL Coder™ User's Guide

© COPYRIGHT 2012-2020 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

### **Revision History**

| March 2012     | Online only | New for Version 3.0 (R2012a)                    |

|----------------|-------------|-------------------------------------------------|

| September 2012 | Online only | Revised for Version 3.1 (R2012b)                |

| March 2013     | Online only | Revised for Version 3.2 (R2013a)                |

| September 2013 | Online only | Revised for Version 3.3 (R2013b)                |

| March 2014     | Online only | Revised for Version 3.4 (R2014a)                |

| October 2014   | Online only | Revised for Version 3.5 (R2014b)                |

| March 2015     | Online only | Revised for Version 3.6 (R2015a)                |

| September 2015 | Online only | Revised for Version 3.7 (R2015b)                |

| October 2015   | Online only | Rereleased for Version 3.6.1 (Release 2015aSP1) |

| March 2016     | Online only | Revised for Version 3.8 (R2016a)                |

| September 2016 | Online only | Revised for Version 3.9 (R2016b)                |

| March 2017     | Online only | Revised for Version 3.10 (Release 2017a)        |

| September 2017 | Online only | Revised for Version 3.11 (R2017b)               |

| March 2018     | Online only | Revised for Version 3.12 (Release 2018a)        |

| September 2018 | Online only | Revised for Version 3.13 (Release 2018b)        |

| March 2019     | Online only | Revised for Version 3.14 (Release 2019a)        |

| September 2019 | Online only | Revised for Version 3.15 (Release 2019b)        |

| March 2020     | Online only | Revised for Version 3.16 (Release 2020a)        |

|                |             |                                                 |

## **HDL Code Generation from MATLAB**

| Functions Supported for HDL Code Gener                                                   | ati       |

|------------------------------------------------------------------------------------------|-----------|

|                                                                                          |           |

| Functions Supported for HDL Code Generation — Alphabetical List                          |           |

|                                                                                          |           |

| Functions Supported for HDL Code Generation — Categorical List                           |           |

|                                                                                          |           |

| Arithmetic Operations in MATLAB                                                          |           |

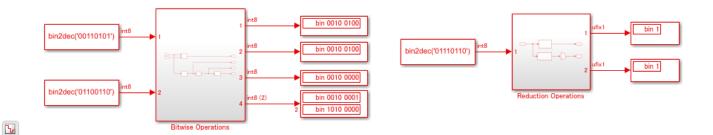

| Bitwise Operations in MATLAB                                                             |           |

| Complex Numbers in MATLAB                                                                |           |

| Control Flow in MATLAB                                                                   | 1         |

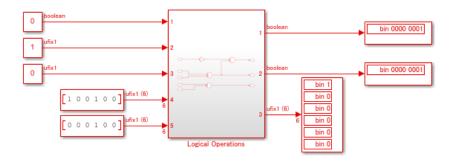

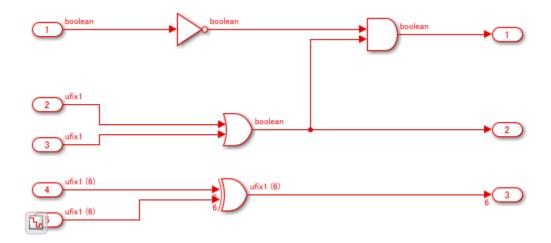

| Logical Operators in MATLAB                                                              | -         |

| Arrays in MATLAB                                                                         | 1         |

| Fixed-Point Designer                                                                     | 1         |

| Supported MATLAB Data Types, Operators, and Control Flow Statements Supported Data Types |           |

| Supported Operators                                                                      |           |

| Control Flow Statements                                                                  |           |

| Persistent Variables and Persistent Array Variables                                      |           |

| Persistent Variables                                                                     |           |

| Persistent Array Variables                                                               |           |

| Complex Data Type Support                                                                |           |

| Declaring Complex Signals                                                                |           |

|                                                                                          |           |

| Conversion Between Complex and Real Signals                                              | 2         |

| Conversion Between Complex and Real Signals Support for Vectors of Complex Numbers       | 2         |

| Conversion Between Complex and Real Signals Support for Vectors of Complex Numbers       | 2         |

| Conversion Between Complex and Real Signals Support for Vectors of Complex Numbers       | 2 2 2 2 2 |

| Conversion Between Complex and Real Signals                                              | 2         |

| Limitations of HDL Code Generation for System Objects          |

|----------------------------------------------------------------|

| System object Examples for HDL Code Generation                 |

| Predefined System Objects Supported for HDL Code Generation    |

| Predefined System Objects in MATLAB Code                       |

| Predefined System Objects in the MATLAB System Block           |

| Load constants from a MAT-File                                 |

| Generate Code for User-Defined System Objects                  |

| How To Create A User-Defined System object                     |

| User-Defined System object Example                             |

| Map Matrices to ROM                                            |

| Fixed-Point Bitwise Functions                                  |

| Fixed-Point Run-Time Library Functions                         |

| Fixed-Point Function Limitations                               |

| Model State with Persistent Variables and System Objects       |

| Bitwise Operations in MATLAB for HDL Code Generation           |

| Bit Shiftting and Rotation                                     |

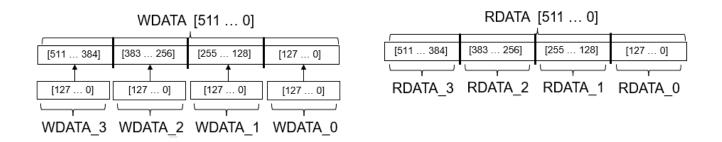

| Bit Slicing and Bit Concatenation                              |

| Guidelines for Writing MATLAB Code to Generate Efficient HDL   |

| Code                                                           |

| MATLAB Design Requirements for HDL Code Generation             |

| Guidelines for Writing MATLAB code                             |

| For-Loop Best Practices for HDL Code Generation                |

| Monotonically Increasing Loop Counters                         |

| Persistent Variables in Loops                                  |

| Persistent Arrays in Loops                                     |

| MATLAB Test Bench Requirements and Best Practices for HDL Code |

| Generation                                                     |

| What Is a MATLAB Test Bench?                                   |

| MATLAB Test Bench Requirements                                 |

| MATLAB Test Bench Best Practices                               |

| ATLAB Best Practices and Design Patterns for HDL               |

| General                                                        |

|                                                                |

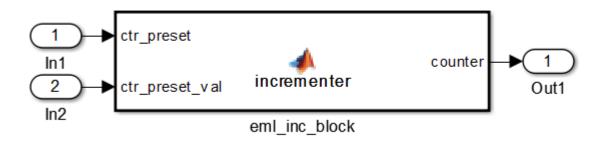

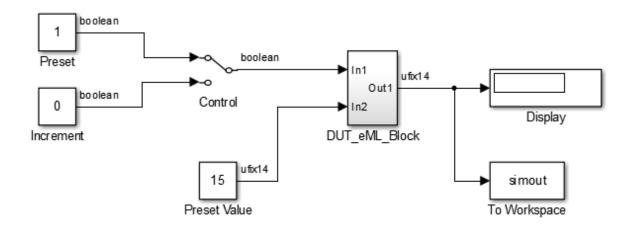

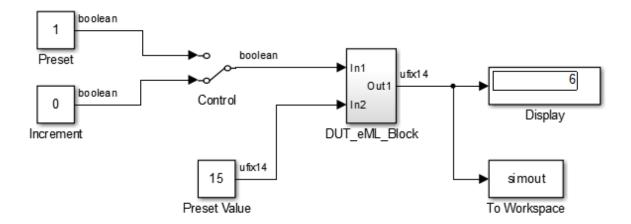

| Model a Counter for HDL Code Generation                        |

| MATLAB Counter                                                 |

| MATLAB Code for the Counter                                    |

| Best Practices in this Example                                 |

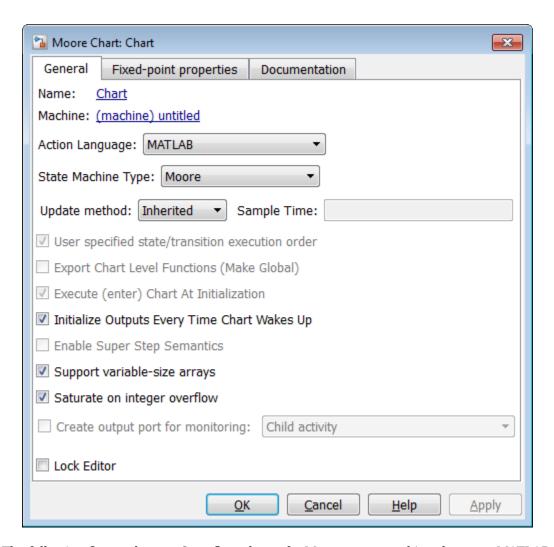

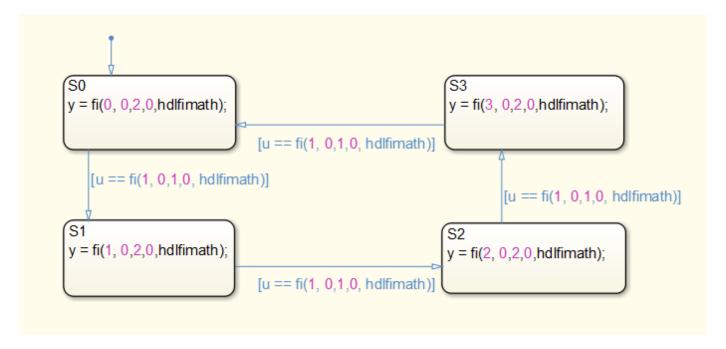

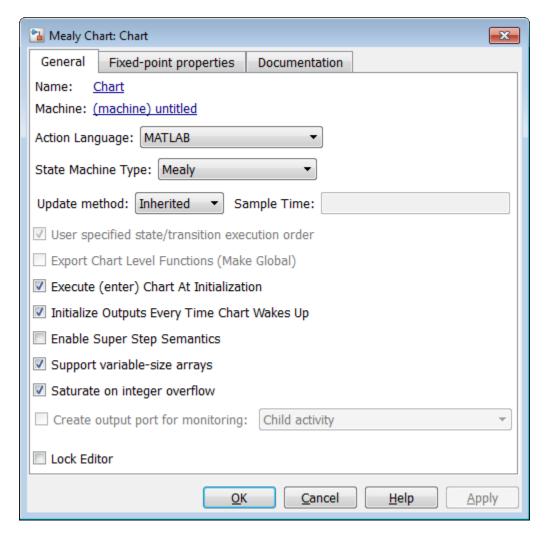

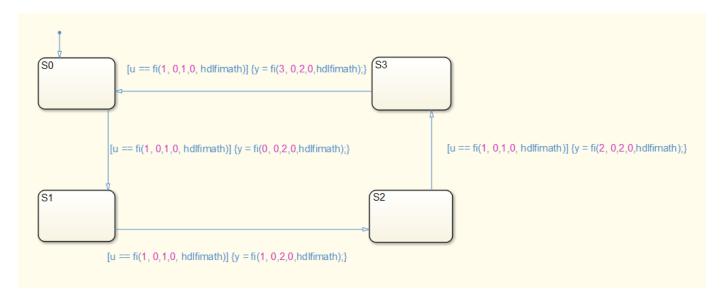

| Model a State Machine for HDL Code Generation                  |              |

|----------------------------------------------------------------|--------------|

| MATLAB State Machines                                          |              |

| MATLAB Code for the Mealy State Machine                        |              |

| MATLAB Code for the Moore State Machine                        |              |

| Best Practices                                                 | 3-/          |

| Generate Hardware Instances For Local Functions                |              |

| MATLAB Local Functions                                         |              |

| MATLAB Code for mlhdlc_two_counters.m                          | 3-8          |

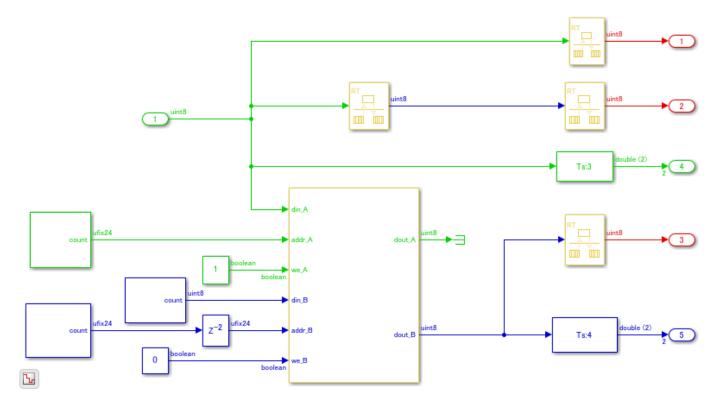

| Implement RAM Using MATLAB Code                                |              |

| Implementation of RAM                                          | 3-10         |

| Implement RAM Using a Persistent Array or System object Proper | 2 4 4        |

| Implement RAM Using hdl.RAM                                    |              |

| Fixed-Point Con                                                | version      |

| Specify Type Proposal Options                                  | 4-2          |

| Log Data for Histogram                                         | <b>4-</b> 5  |

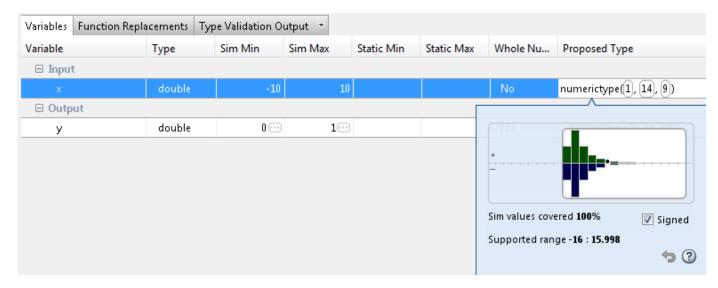

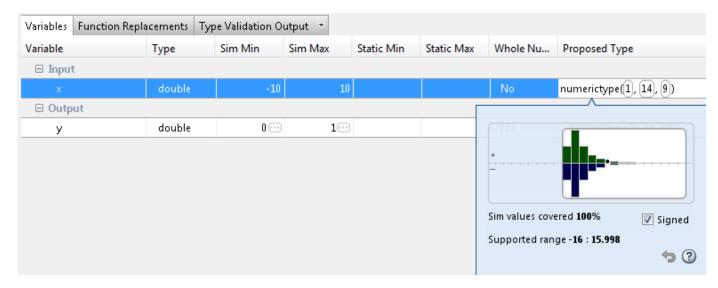

| View and Modify Variable Information                           | 4-7          |

| View Variable Information                                      |              |

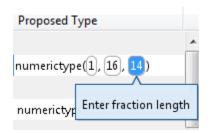

| Modify Variable Information                                    |              |

| Revert Changes                                                 |              |

| Promote Sim Min and Sim Max Values                             |              |

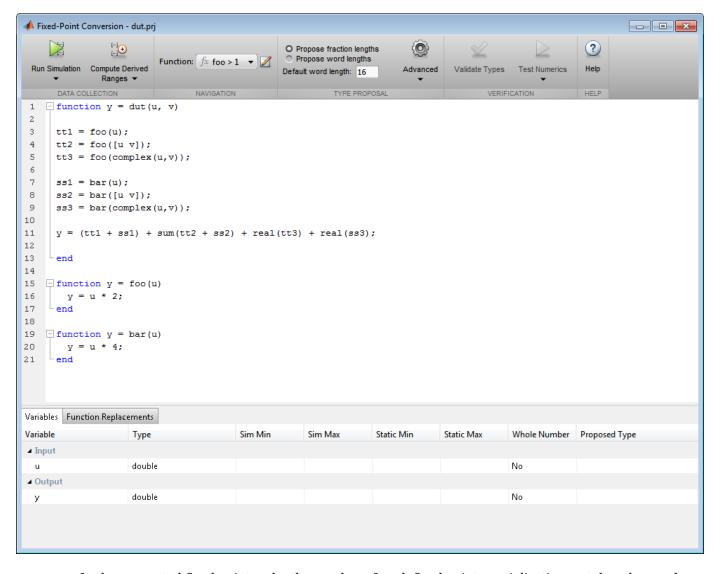

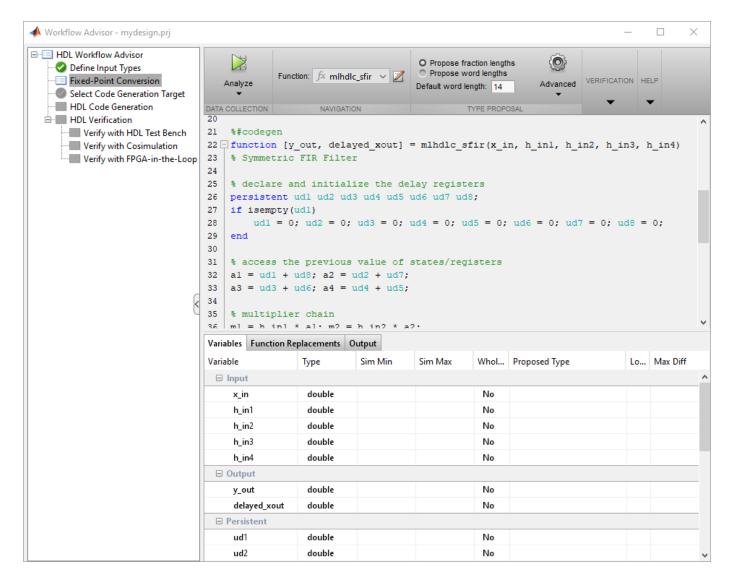

| Automated Fixed-Point Conversion                               | 4-9          |

| License Requirements                                           |              |

| Automated Fixed-Point Conversion Capabilities                  | 4-9          |

| Code Coverage                                                  | 4-10         |

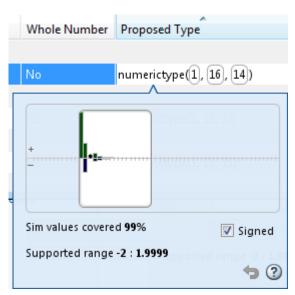

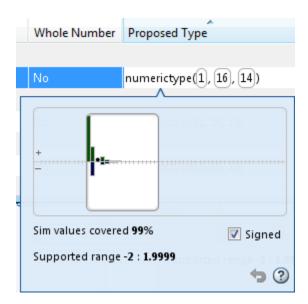

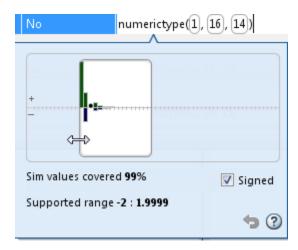

| Proposing Data Types                                           | 4-12         |

| Locking Proposed Data Types                                    | 4-13         |

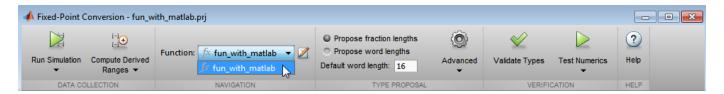

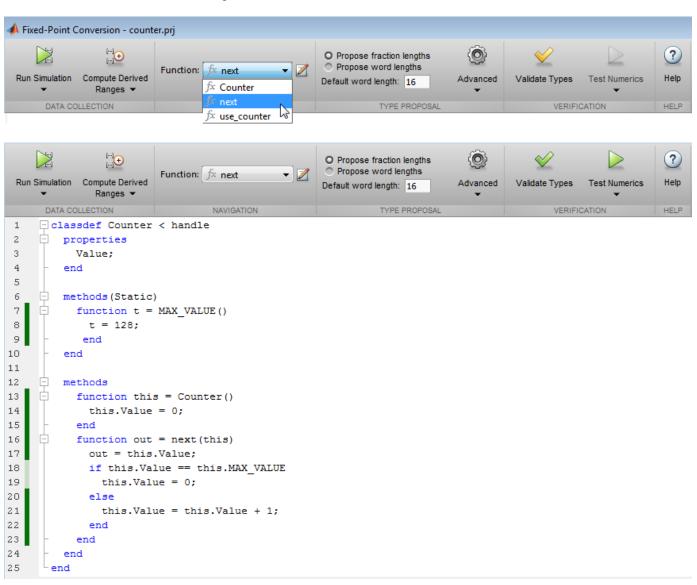

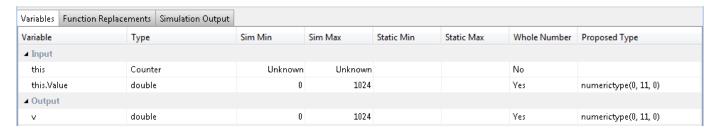

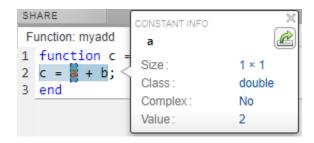

| Viewing Functions                                              |              |

| Viewing Variables                                              |              |

| Histogram                                                      |              |

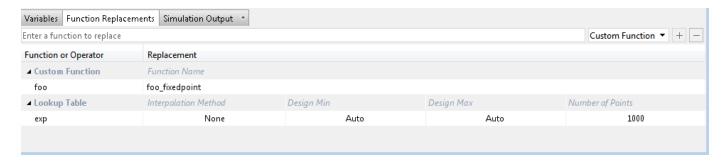

| Function Replacements                                          |              |

| Validating Types                                               |              |

| Testing Numerics                                               |              |

| Detecting Overflows                                            | 4-21         |

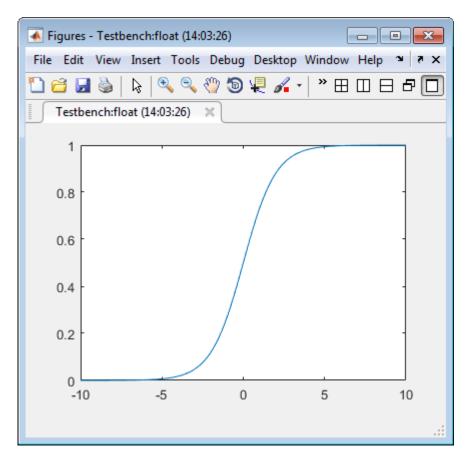

| Custom Plot Functions                                          | <b>4-2</b> 3 |

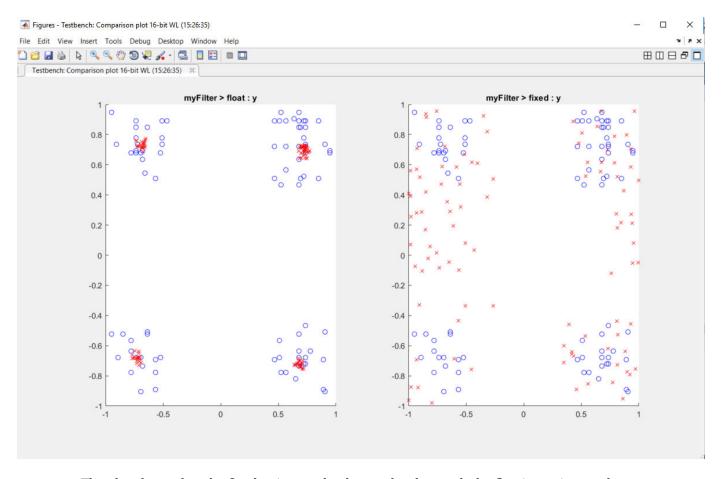

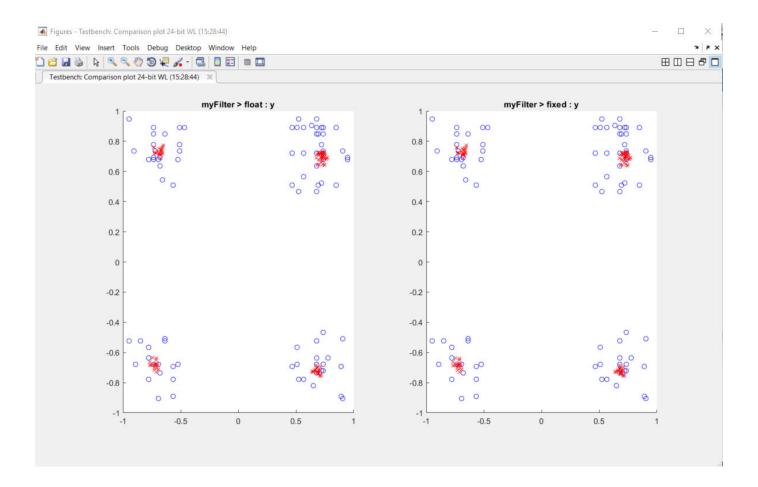

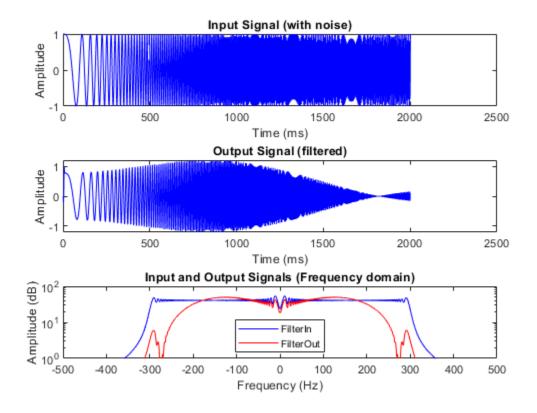

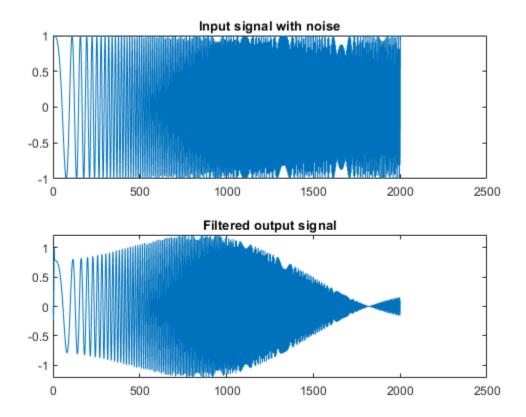

| Visualize Differences Between Floating-Point and Fixed-Point   |              |

| Results                                                        | 4-24         |

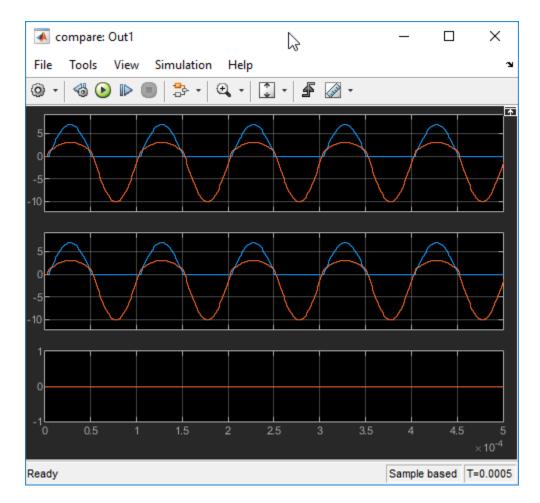

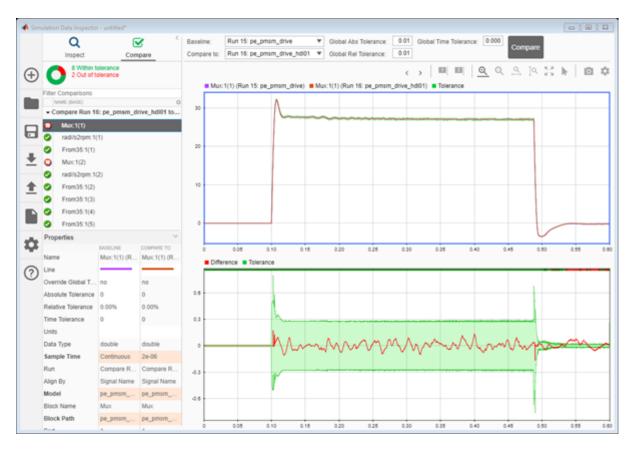

| Inspecting Data Using the Simulation Data Inspector            | 4-29         |

| What Is the Simulation Data Inspector?                         | <b>4-2</b> 9 |

| Import Logged Data                                             |              |

| Export Logged Data                                             | 4-29         |

| Create Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Group Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-29<br>4-29                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Comparison Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                  |

| Enabling Plotting Using the Simulation Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Enable Plotting Using the Simulation Data Inspector 4-31 From the UI 4-31 From the UI 4-31 From the Command Line 4-31 Replacing Functions Using Lookup Table Approximations 4-32 Replace a Custom Function with a Lookup Table 4-33 Using the HDL Coder App 4-33 From the Command Line 4-36 Replace the exp Function with a Lookup Table 4-39 From the UI 4-39 From the UI 4-39 From the Uin 4-39 From the Command Line 4-45 Enable the Highlight Option in a Project 4-45 Enable the Highlight Option at the Command Line 4-45 Stowaway Doubles 4-45 Expensive Fixed-Point Operations 4-45 Expensive Fixed-Point Operations 4-45 Expensive Fixed-Point Operations 4-45 Stowaway Singles 4-45 Expensive Fixed-Point Operations 5-3 Add Files to the Project 5-2 Open an Existing Project 5-3 Add Files to the Project 5-3 Add Files to the Project 5-4 Why You Must Specify Input Properties 5-4 Why You Must Specify Input Properties 5-4 Properties of Secifying Properties of Primary Inputs 5-5 Methods for Defining Properties of Primary Inputs 5-5 Methods Generation from System Objects 5-14 Code Generation Reports 5-18 Report Location 5-18 Report Location 5-18 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Enable Plotting Using the Simulation Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| From the UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Save and Load Simulation Data hispector Sessions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-30                                                                               |

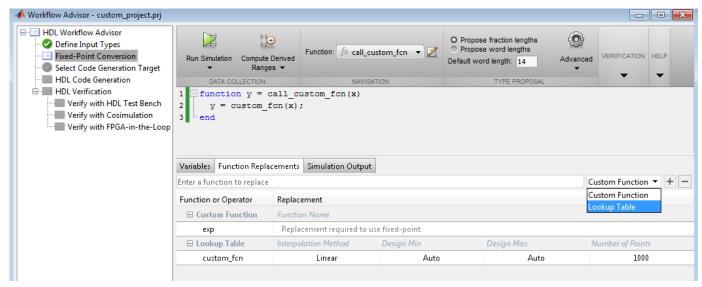

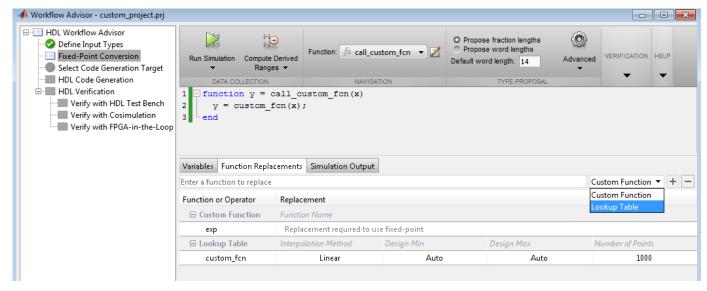

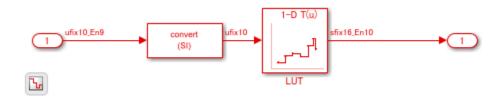

| Replacing Functions Using Lookup Table Approximations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Replace a Custom Function with a Lookup Table         4-32           Replace a Custom Function with a Lookup Table         4-33           Using the HDL Coder App         4-36           From the Command Line         4-36           Replace the exp Function with a Lookup Table         4-39           From the UI         4-39           From the Command Line         4-42           Data Type Issues in Generated Code         4-45           Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Expensive Fixed-Point Operations         4-45           Expensive Fixed-Point Operations         4-45           Create and Set Up Your Project         5-2           Create and Set Up Your Project         5-2           Create and Set Up Your Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Properties to Specify Input Properties of Prim                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Replace a Custom Function with a Lookup Table         4-33           Using the HDL Coder App         4-33           From the Command Line         4-36           Replace the exp Function with a Lookup Table         4-39           From the UI         4-39           From the Command Line         4-42           Data Type Issues in Generated Code         4-45           Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Expensive Fixed-Point Operations         4-45           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           When to Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | From the Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-31                                                                               |

| Using the HDL Coder App                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Replacing Functions Using Lookup Table Approximations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-32                                                                               |

| From the Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

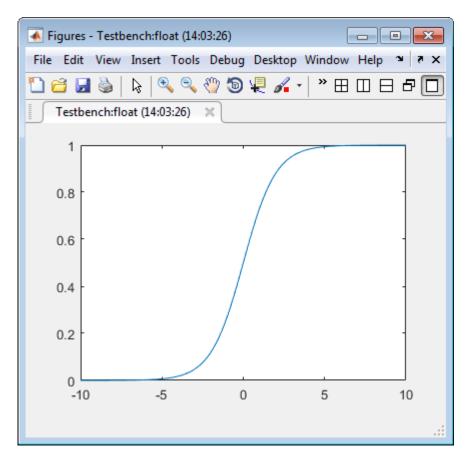

| Replace the exp Function with a Lookup Table         4-39           From the UI         4-39           From the Command Line         4-42           Data Type Issues in Generated Code         4-45           Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Expensive Fixed-Point Operations         4-45           Create and Set Up Your Project         5-2           Copen an Existing Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by         Using the Workflow Advisor         5-7           HDL Code Generation from System Objects         5-                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| From the UI         4-39           From the Command Line         4-42           Data Type Issues in Generated Code         4-45           Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Properties to Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by<br>Using the Workflow Advisor         5-7           HDL Code Generation Reports         5-18           Report Generation         5-18           Report Generation         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | From the Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-36                                                                               |

| From the UI         4-39           From the Command Line         4-42           Data Type Issues in Generated Code         4-45           Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Properties to Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by<br>Using the Workflow Advisor         5-7           HDL Code Generation from System Objects         5-18           Report Generation         5-18           Report Generation         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Replace the exp Function with a Lookup Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-39                                                                               |

| Prom the Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | From the UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-39                                                                               |

| Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Code Generation           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by         Using the Workflow Advisor         5-7           HDL Code Generation Reports         5-18           Report Generation         5-18           Report Generation         5-18           Report Location         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-42                                                                               |

| Enable the Highlight Option in a Project         4-45           Enable the Highlight Option at the Command Line         4-45           Stowaway Doubles         4-45           Stowaway Singles         4-45           Expensive Fixed-Point Operations         4-45           Code Generation           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Methods For Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by Using the Workflow Advisor         5-7           HDL Code Generation Reports         5-18           Report Generation         5-18           Report Generation         5-18           Report Location         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data Type Issues in Generated Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-45                                                                               |

| Enable the Highlight Option at the Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Stowaway Singles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Create and Set Up Your Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 5 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                    |

| Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Methods Generation and FPGA Synthesis from MATLAB by         Using the Workflow Advisor         5-7           HDL Code Generation from System Objects         5-14           Code Generation Reports         5-18           Report Generation         5-18           Report Location         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Code Generation           Create and Set Up Your Project         5-2           Create a New Project         5-2           Open an Existing Project         5-3           Add Files to the Project         5-3           Specify Properties of Entry-Point Function Inputs         5-4           When to Specify Input Properties         5-4           Why You Must Specify Input Properties         5-4           Properties to Specify         5-4           Rules for Specifying Properties of Primary Inputs         5-5           Methods for Defining Properties of Primary Inputs         5-5           Basic HDL Code Generation and FPGA Synthesis from MATLAB by         Using the Workflow Advisor         5-7           HDL Code Generation from System Objects         5-14           Code Generation Reports         5-18           Report Generation         5-18           Report Location         5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

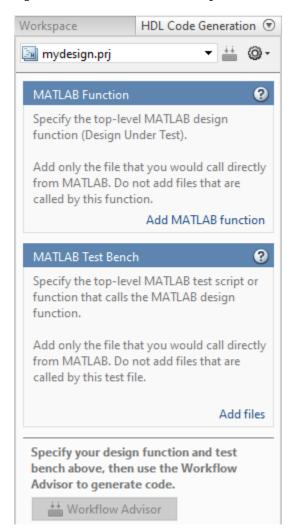

| Create a New Project       5-2         Open an Existing Project       5-3         Add Files to the Project       5-3         Specify Properties of Entry-Point Function Inputs       5-4         When to Specify Input Properties       5-4         Why You Must Specify Input Properties       5-4         Properties to Specify       5-4         Rules for Specifying Properties of Primary Inputs       5-5         Methods for Defining Properties of Primary Inputs       5-5         Basic HDL Code Generation and FPGA Synthesis from MATLAB by       5-7         HDL Code Generation from System Objects       5-14         Code Generation Reports       5-18         Report Generation       5-18         Report Location       5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| Open an Existing Project 5-3 Add Files to the Project 5-3 Add Files to the Project 5-3  Specify Properties of Entry-Point Function Inputs 5-4 When to Specify Input Properties 5-4 Why You Must Specify Input Properties 5-4 Properties to Specify 5-4 Rules for Specifying Properties of Primary Inputs 5-5 Methods for Defining Properties of Primary Inputs 5-5  Basic HDL Code Generation and FPGA Synthesis from MATLAB by Using the Workflow Advisor 5-7  HDL Code Generation from System Objects 5-14  Code Generation Reports 5-18 Report Generation 5-18 Report Location 5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Code Genera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tion                                                                               |

| Add Files to the Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Create and Set Up Your Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-2                                                                                |

| When to Specify Input Properties 5-4 Why You Must Specify Input Properties 5-4 Properties to Specify 5-4 Rules for Specifying Properties of Primary Inputs 5-5 Methods for Defining Properties of Primary Inputs 5-5  Basic HDL Code Generation and FPGA Synthesis from MATLAB by Using the Workflow Advisor 5-7  HDL Code Generation from System Objects 5-14  Code Generation Reports 5-18 Report Generation 5-18 Report Location 5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Create and Set Up Your Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-2<br>5-2                                                                         |

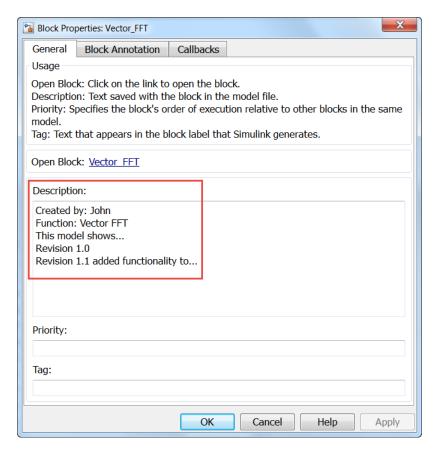

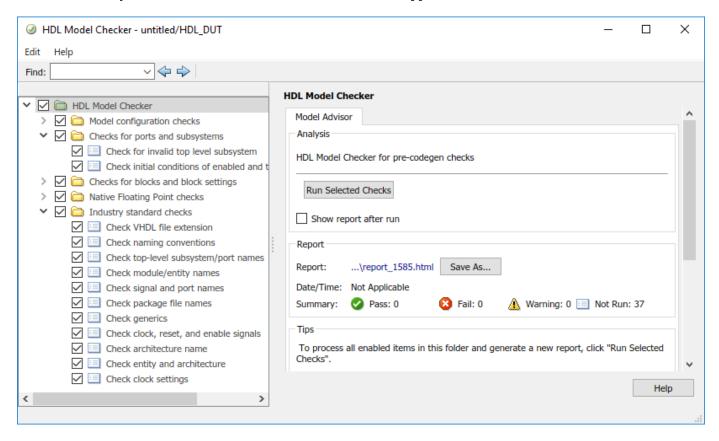

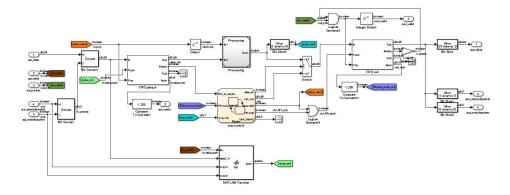

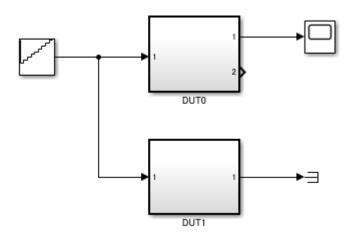

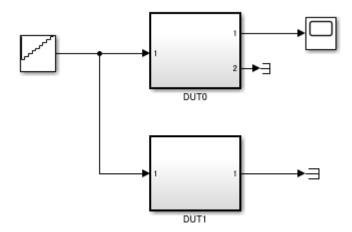

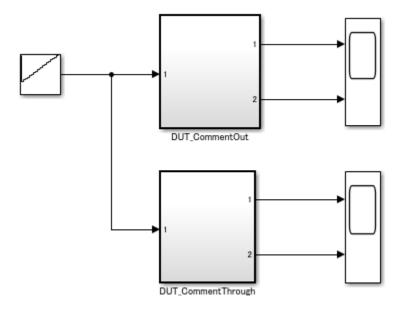

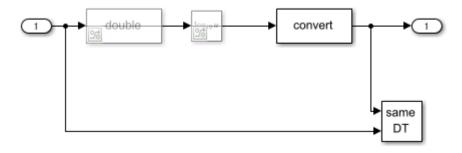

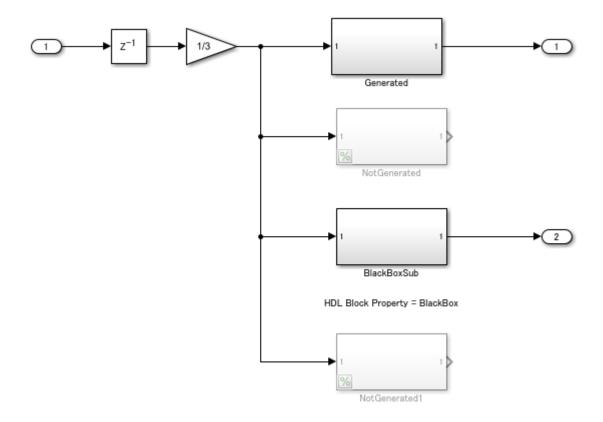

| When to Specify Input Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Create and Set Up Your Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-2<br>5-2<br>5-3                                                                  |